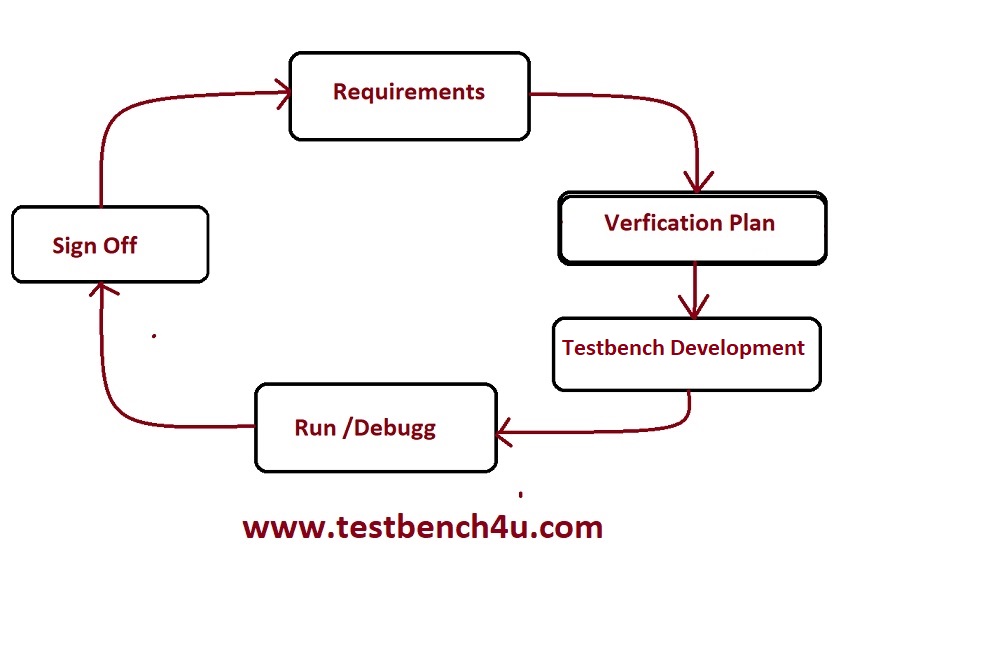

How to move from specification to sign off for hardware design ?

Career Oppurtunity, Companies Related Questions, Formal Verification, Functional Verification 0 CommentsHow do we move from given specification to sign off for hardware

Logic designer writes the specification for given design.

Verification engineer goes through the specification provided by logic designer.

He/She makes verification plan for the given specification of the logic design.

Next step is to develop testbench.

After developing testbench , it has to run.

Run can result into fail or pass, in case fail, it needs to debugged.

If there is 100% functional coverage , 100 % code coverage , chip goes for fabrication.

If the coverage goal is not achieved , then steps need to repeated.

Then there has to have fixing in testbench, either new stimulus or new check .

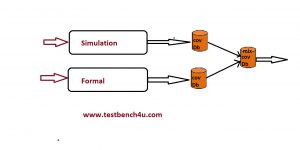

Test plan for formal and simulation and its coverage goal.

In order to have good verification , both formal and simulation environment is built. DV engineer decides what part of design will have formal and what part of design will have simulation environment.

So both environment will have coverage, coverage is mixed to check all the functionality.

How can we say verification is completed ??

To know that few things need to checked ?

Test bench , does it have good quality check ?

How do we you know the test bench is of good quality ?

if you write good quality stimulus ?

does it have enough stimulus ?

what is being exercised ?

Lets See a Example

RTL

if(enable)

signal A <=1’b1

So for this part of rtl , DV engineer writes an assertions to check its functionality .

Assertion result from formal tool is reachable and proven.

and now seeing through coverage tool, and trying to answer following question above.

Coverage tool has two part, activation and observation

activation means , is this assertion activating above rtl code while checking it ,

if the answer is no,it means no check is done , if yes this assertion is activated this piece of rtl code , it brings this bring to observation. so is this piece of code observed , if there is change in logic code , assertion will fail. So if it is not observed it means ,it has bad check. if it is observed , it means it has good quality check.

So we have to have good quality testbench and good coverage .

In final test bench is reviewed , is any thing missing or written multiple check of same interface , redundant stuff is removed.