MESI protocol practical Example

Companies Related Questions, Computer Archtecture 0 CommentsConsider a situation in which two processors in an SMP configuration, over time, require access to the same line of data from main memory. Both processors have a cache and use the MESI protocol. Initially, both caches have an invalid copy of the line.

If this is the start of a sequence of accesses, draw the subsequent figures for the following sequence

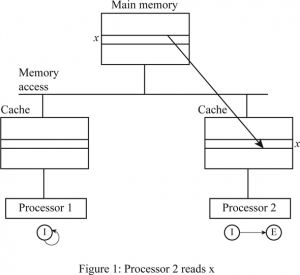

1. P2 reads x.

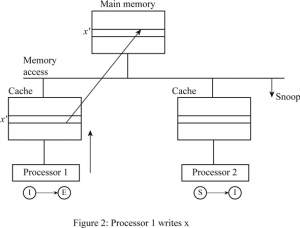

2. P1 writes to x (for clarity, label the line in P1’s cache x′).

3. P1 writes to x (label the line in P1’s cache x″).

4. P2 reads x.

Explanation

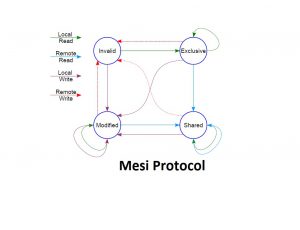

How Mesi Protocol works , it is shown in below picture

it has 4 states : Modified, Exclusive Shared, Invalid based on read or write request it changes to different states.You can read about all states here

Lets Execute the problem.

1. P2 reads x.

Initially both processor’s caches will be in invalid states, so when p2 reads X ,p2 cache brings the data in its cache from memory and it goes to exclusive state. P1 cache state is in invalid.

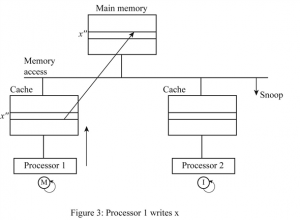

2. P1 writes to x (for clarity, label the line in P1’s cache x′).

When P1 writes to x(x’) it will be like this , it will go in modified state , and broadcast invalid to x address.

3. P1 writes to x (label the line in P1’s cache x″).

P1 is in modified state , P2 will invalidate its entry and goes to invalid state

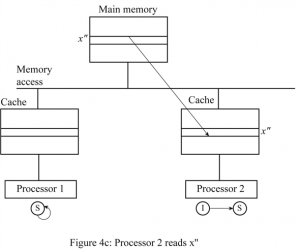

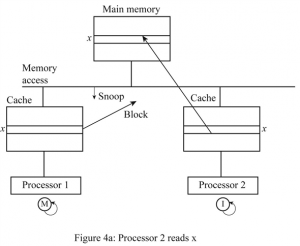

4. P2 reads x.

A.When P2 tries to see the data in its cache , it is not there , so it tries to access the data from memory. Memory is not updated for x

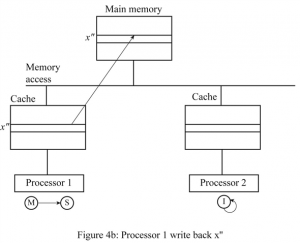

4b Memory is updated by processor 1. Processor 1 goes to shared state.

4 c processor 2 reads data from main memory and goes to shared state