What is TLB (TRANSLATION LOOK ASIDE BUFFER )

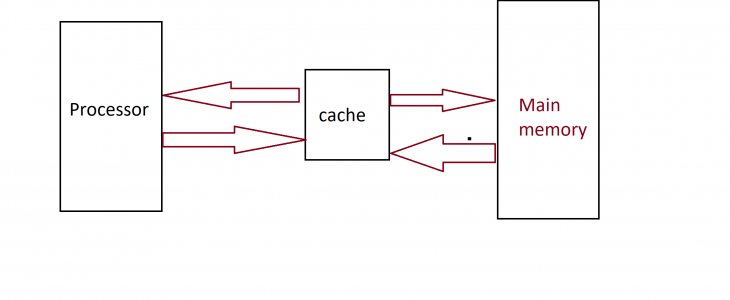

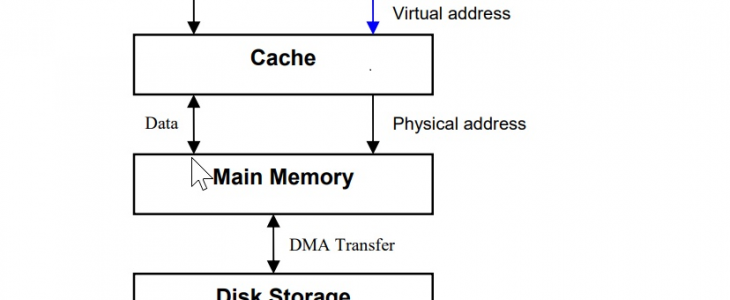

Companies Related Questions, Computer Archtecture 0 CommentsThis portion consists of the page table entries that correspond to the most recently accessed pages. A small cache, usually called the Translation Lookaside Buffer (TLB) is incorporated into the MMU for this purpose. The operation of the TLB with respect to the page table in the main memory is essentially the same as the