Fifo (synchronous ) UVM test bench

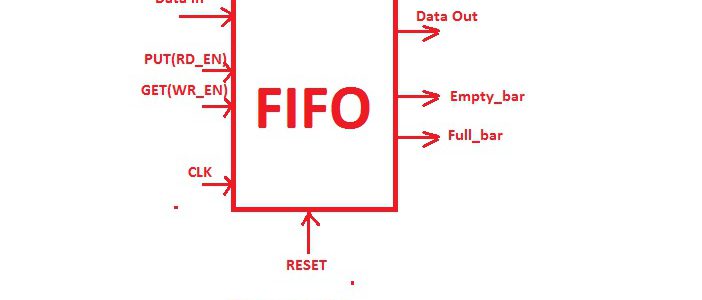

Functional Verification, Soc(System on Chip), System Verilog, UVM 0 CommentsDefinition : Fifo (synchronous ) The Synchronous FIFO has a single clock port for both data-read and data-write operations, it means it is used for synchronising across two process when two process are running on same clock. One source writes to the FIFO and the other sources reads out the FIFO where it sees the order